Interrupt On Change sur pin RA5 18F27K42 (MikroC)

Hardware :

Base 18F27K42

HARDWARE

Alimentation VCC= 3.6V

Carte BASE 18F27K42

Entree testée =RA5 input !

Led sur RA4 pour signaler l'IT IOC

UART1 TX sur RC6

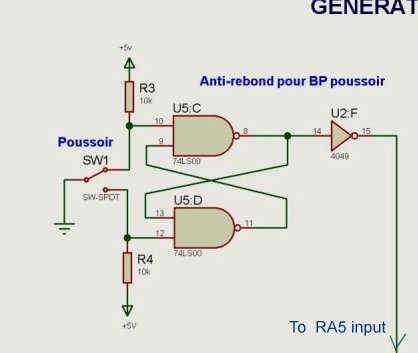

Utilisation de mon generateur BF , avec mode Coup par coup via un Bouton Poussoir

pour éviter tout rebonds sur le signal d'entree RA5.

Contrairement aux Anciens PIC (qui ne geraient que le PORTB) ,

avec celui ci on peut genérer une interruption via N'IMPORTE QUELLE pin du MCU

Extrait datasheet :

18.0 INTERRUPT-ON-CHANGE

Interruption sur changement d'etat sur n'importe quelle broche (Pin) d'un PORT.

18.1 Enabling the Module

Validation du registre PIEx pour permettre la generation d'une interruption sur une broche d'un PORT

le bit IOCIE correspondant du registre PIEx doit etre armé pour generer l'interruption.

Ceci n'empeche pas la detection de se faire ..

18.2 Individual Pin Configuration

Pour chaque pin de PORT, un detecteur de front Montant ou Descendant est présent

Pour valider une detection de front Montant sur une Pin , le bit associé du registre IOCxP (P comme Positif!) est mis à 1 .

Pour valider une detection de front Descendant sur une Pin , le bit associé du registre IOCxN (N comme Negatif!)est mis à 1 .

Une pin (broche) peut etre configuée en detection Front Montant ET Decendant , en armant (Mise à 1 ) le bit des 2 registres

correspondant IOCxP ET IOCxN

18.3 Interrupt Flags

les bits IOCAFx, IOCBFx, IOCCFx et IOCEF3 sont situés dans les registres respectifs IOCAF, IOCBF, IOCCF and IOCEF

leurs etats 0 ou 1 , reflete l'etat Interrupt On Change du PORT concerné.

Si un changement de front attendu est detecté sur la broche (Pin) validée en detection , le bit IOCIE est armé (mis à 1)

=> interruption autorisée

le bit IOCIF est aussi armé, il reflete l'etat de toutes le spin concernée sur les PORTS IOCAFx, IOCBFx,IOCCFx,IOCEF3_bit

18.4 Clearing Interrupt Flags RAZ des drapeaux

L'eat individuel des drapeaux representant les entrees du PORT (IOCAFx, IOCBFx, IOCCFx et IOCEF3 bits),

peut etre respectivement remis à zero .

Si une autre detection de front est detectée pendant la remise à zero,

le flag associé est à nouveau remis à un.

Pour s'assurer qu'aucun Front ne soit perdu , pendant la remise à zero du Flag ( en cours de traitement)

Seule une operation utilisant un MASQUE permettant d'isoler le(s) bit(s) connu comme ayant changé

doit etre réalisée.

exemple de sequence :

MOVLW 0xff

XORWF IOCAF, W

ANDWF IOCAF, F

le test ci-dessu n'est pas convainquant ..pour ma part .