version 0.0 :

27 juin 2019

rev ......

Le PIC

16(F) ou (L)1847 :

en connectique Dip18

Utilisé avec Fosc Interne =32Mhz ( 8Mhz x 4PLL)

Available RAM: 1008 [bytes], Available ROM: 8192 [bytes])

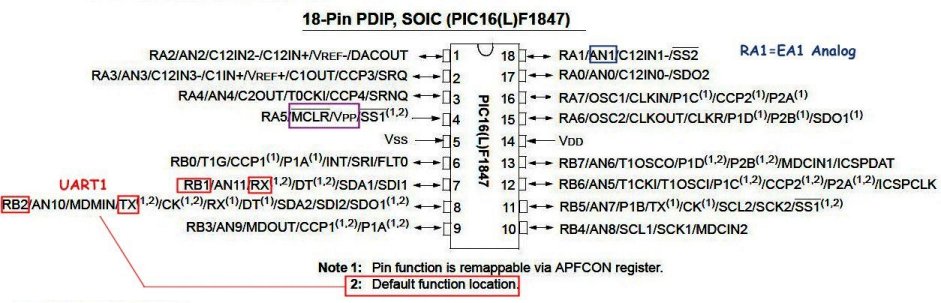

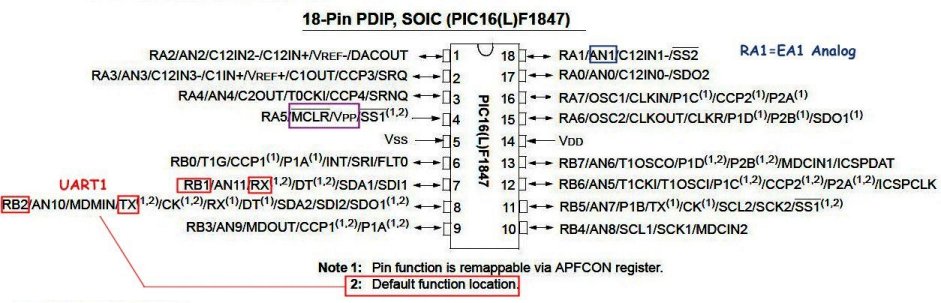

Pinout

Hardware :

Test du Generateur programmable de

Frequence

datasheet DS40001453E

6.0 REFERENCE CLOCK MODULE

The reference clock module is controlled by the CLKRCON register

(Register 6-1) and is enabled when

setting the CLKREN bit. To output the divided clock signal to the

CLKR port pin, the CLKROE bit must be

set. The CLKRDIV<2:0> bits enable the selection of eight

different clock divider options. The

CLKRDC<1:0> bits can be used to modify the duty cycle of

the output clock(1).

The CLKRSLR bit controls slew rate limiting.

Le 16F1847 utilise son horloge interne FOSC=8MHz x PLL => 8x 4

= 32MHz

au depart OSCTUNE=0 ( valeur nominale)

La sortie CLKR est affectée d'office à la pin RA6 ( ne pas

activer CLOCKOUT_EN dans la config bits !)

Suivant la valeur de DIV ,on obtient 8 frequences de sortie

possibles

Suivant la valeur de DUT , on obtient 25 , 50 , ou 75% de rapport

cyclique ( sans modifier la frequence)

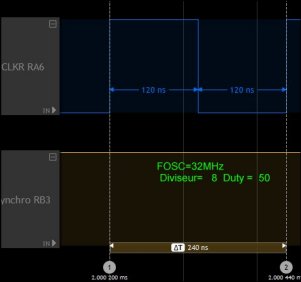

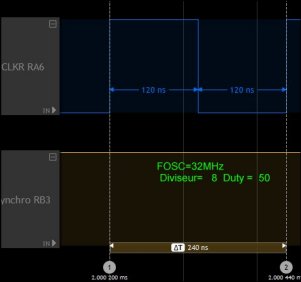

J'utilise SQA IKALOGIC Analyser pour les mesures (echantillonnage

des 4 voies à 50MHz)

la sortie RB3est utilisée pour declencher les mesures

L'UART1 RB1=RX et RB2=TX permet l'affichage et la saisie des

parametres DIV et DUT

relation Index parametre d'entrée et parametre appliqué pour le

registre CLKRCON

unsigned char Diviseur,Duty;

unsigned char Gamme_Diviseur[]={1,2,4,8,16,32,64,128};

unsigned char Gamme_Duty[]={0,25,50,75};

exemple à l'init programme :

Duty=2; //50%

CLKRCON= CLKRCON & 0xE7;

CLKRCON= CLKRCON | (Duty<<3) ; // Duty 1 à 3

//CLKRDIV<2:0> Reference Clock Divider bits

Diviseur=4; // 16

CLKRCON=CLKRCON & 0xF8;

CLKRCON=CLKRCON | Diviseur; // diviseur 1 à 7 ( 1 à 128)

La commande clavier se fait par les mots clés DIV=x ou DUT=y

L'UART recoit les commandes par interruption.

L'indice du parametre est verifié, puis appliqué ,si dans les

limites imposées.

Un test Specifique a été fait avec OSCTUNE ,mini et maxi

Resultats :

Check avec analyser

|

|

|

| DIV by 4 et Duty_Cycle=50% |

DIV by 8 et Duty_Cycle=50% |

DIV by 128et Duty_Cycle=50% |

|

|

|

| OSCTUNE pour FOSC mini |

OSCTUNE pour FOSC nominale |

OSCTUNE pour FOSC Maxi |

Autres valeurs de DUT

|

|

| Diviseur=128 Duty_Cycle=25% |

Diviseur=128 Duty_Cycle=75% |

Le projet MikroC (version 7.40 )

16F1847_UART_RB2_RB1_RX_Interrupt_test_CLRKout_190627.zip

source MikroC:

_16F1847_UART_RB2_RB1_RX_Interrupt_test_CLRKout_190627.c

Chargeur :

16F1847_test_CLKROut_RA6_Uart_RB2_RB1_RX_interrupt_190627.hex

et on en fait QUOI

? concretement ?

....Generateur de frequence ajustable à +-3% via la valeur de

OSCTUNE , modifiable par clavier, ou par touches directes sur

entrees MCU.

...Gamme de frequence davantage variable , avec la combinaison de

reglage FOSC 500Khz à 16 MHz

..et si on rajoutait un mini DDS sur la sortie DAC RA2 pour avoir

un petit Gene BF sinus ? en plus

.

Retour à l'index general